R7D - Capstone

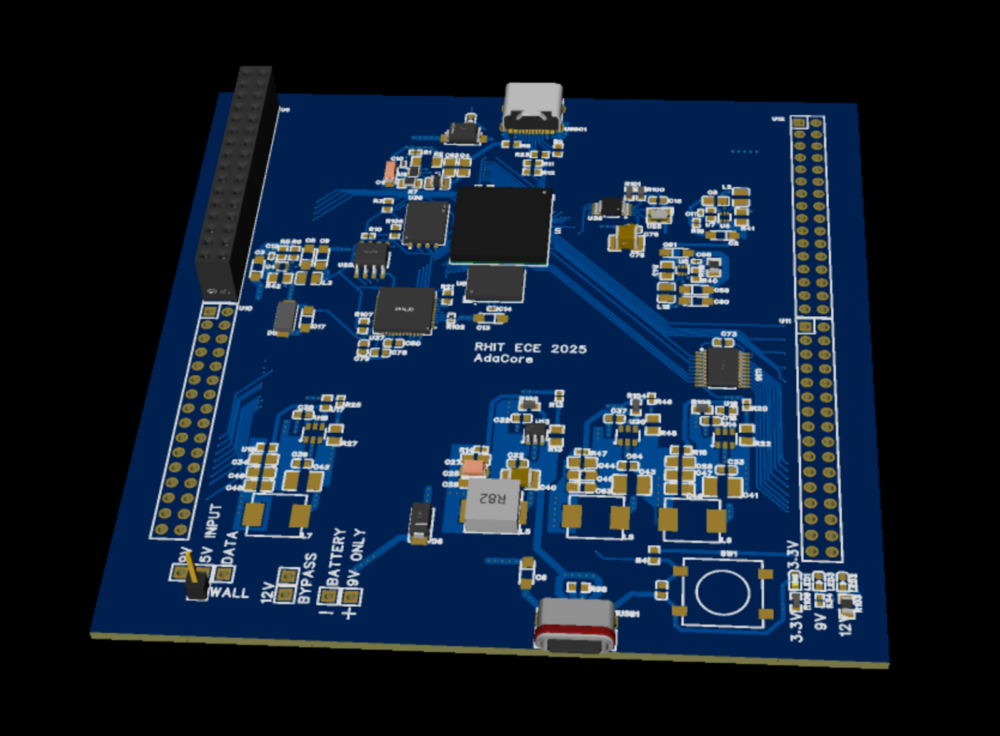

R7D, designed by a group of students is the first iteration of a Lattice ECP5 FPGA board enabling an Ada-first, Alire-managed ecosystem with flexible power, SRAM/FRAM, and modular I/O.

Rose-Hulman Institute of Technology

R7D is the first iteration of a Lattice ECP5 FPGA development board designed by a group of students (Richard Hsin, Kennedy Olson, Justin Roberts, and Blake Sheppard) from the Rose-Hulman Institute of Technology. With the growing momentum behind open-source gateware and in line with the goals of the GNAT Academic Program, the team set out to design an extensible development board focused on supporting a rich Ada-based ecosystem, fully managed through Alire, Ada's package manager.

They developed a practical board aimed at solving common prototyping challenges—especially for those working without access to a full lab setup. The design includes essentials like SRAM, FRAM (non-volatile memory), support for multiple standard I/O voltages, a flexible power subsystem (supporting 5V logic and up to 15W power), and modular I/O expansion through 16-, 32-, and 64-pin blocks.

The goal was to address the problems that appear early in hardware projects: dealing with power domains, needing simple and accessible memory, or lacking flexible I/O options. This first version lays the groundwork for further iterations on the hardware and the Ada support infrastructure.

The project was successful and is now moving into a second design phase.